EXPERIMENTAL TELEVISION CENTER LTD.

164 COURT ST.

PINGHAMTON NEW YORK 13901

607-723-9509

Computer-Based Video Synthesizer System

This report summarizes the results of the research and development of a computer controlled video image processing and synthesizing device, a project supported in part by the National Endowment for the Arts and the New York State Council on the Arts.

Dr. Donald McArthur, Systems Design Mr. Walter Wright, Software Development

Mr. Richard Brewster, Systems Construction

October 1977

The Experimental Television Center Ltd. is a not-for-profit educational corporation supported in part by the New York State Council on the Arts and the National Endowment for the Arts.

# EXPERIMENTAL TELEVISION CENTER LTD. 164 COURT ST. BINGHAMTON NEW YORK 13901 607-723-9509

As video image generating, processing and synthesizing systems become increasingly sophisticated, the problem of achieving maximum control over these systems must be addressed. This is particularly relevant to situations in which videomakers work independently and frequently as individuals in the creation of their works. Many video systems provide such a large number of image making variables that manual adjustments within the parameters of each control necessary to obtain desired structures and sequences is not always possible. The artist must then compromise the image to the system. Video synthesizer systems offer an enormous potential for intricate image constructions, but without appropriate control systems the individual artist may not be able to take full advantage of the system to achieve with accuracy the structures desired. Microprocessor systems, it was believed, could provide the necessary control for precision of image structuring if these computer systems could be completely dedicated to the processes of visual art making and be made usable by artists in direct ways.

The primary aim of the Computer-Based Video Synthesizer project was the research and development of such systems with capacity for direct use by artists in the production of independent works. A major design consideration in both hardware and software development concerned the establishment of a holistic system directly related to the requirements of individuals working in the electronic arts and usable by them in their personal work. It was considered important to reduce, as much as possible, the reliance by artists on outside technical support in the production processes because of the difficulties of communication and interpretation and the intimacy of the creative situation. The initial planning for this project began in 1975 with conferences at the Experimental Television Center involving Mr. Ralph Hocking, Mr. Walter Wright, Dr. Donald McArthur and Mr. Richard Brewster of Binghamton, New York and Steina and Woody Vasulka of Buffalo, New York. With support from the National Endowment for the Arts and the New York State Council on the Arts, the project was completed in the Fall of 1977; the resulting system is now operational at the Experimental Television Center and is available for use by artists through the production program at the Center.

An important philosophical consideration throughout the project concerned a humanistic approach to the design and utilization of computer and video systems technologies; one of the initial stages of this project involved the development of methodologies which would guide the construction of complex tools and systems dedicated to the needs of visual artists. To achieve this end, it was essential that artists, programmers and engineers work together in all aspects of the project, each group communicating from its own unique perspective. Artists helped to articulate and define the types of controls which they felt were important in image making. Engineers and programmers frequently introduced image making devices and control methods which had not previously been available; the structural and compositional potentials of these components were completely unexplored. In the design and construction of the hardware there were a number of specific objectives. A flexible and versatile system was important in order

to provide artists with as many options as possible for image generation, processing and control. The present system is modular in design and permits the inclusion or exclusion of discrete components in the assembly of a system specifically tailored to meet the individual requirements of a particular artist or project. Modular and standardized design also allows for the future research and development of new components and the modification of existing hardware and software all of which can be incorporated into the present system with a minimum of effort. The system is capable of interfacing with many video and computer components an increasing number of which are owned by or accessible to individual artists and small arts organizations. For example, the system at the Center is compatible with the system of Steina and Woody Vasulka, and exchanges of software and hardware are possible between Buffalo and Binghamton. Video production requires a fairly powerful microprocessor system which is capable of efficiently handling the large amount of information necessary in the generation and control of image structures. The needs for a powerful system, also low in cost, had to be weighed against the factor of complexity since the system was to be used by individual artists the majority of whom had little or no prior experience with computer hardware or software. The 16 bit system as it was designed and constructed met the criteria of low cost, high power and ease of operation. The hardware made use of commercially available components as much as possible in the interests of efficiency of operation and construction and ease of duplication of the system by artists and arts groups. Many specific components and interfaces. however, had to be designed and constructed specifically for this project since they were either not available commercially or were too costly; many of the commercial components which were available did not meet the specific requirements determined by the nature of the application of the system.

The software development for this project also emphasized a humanistic approach to the use of microprocessor and video systems by artists. The goal of the software research was the development of an interactive language usable by artists. This language had to be understandable to artists so that they could address the computer directly, using language and concepts derived from the visual arts, without the necessity of translation into high level computer languages. The language had to be responsive to the needs of artists, enabling them to manipulate discrete elements of design and compositional structures. Further, it had to allow the artist to intervene at any point in the construction of the composition so details of compositional configurations as well as whole sequences could be easily altered. Precision was felt to be critical; the artist had to be able to develop and score the composition, store, run and edit it in a manner which insured its accuracy and repeatability. It was felt that the language should also provide for the option of programmed randomness and operate in either structured or random modes or a predetermined combination of both modes.

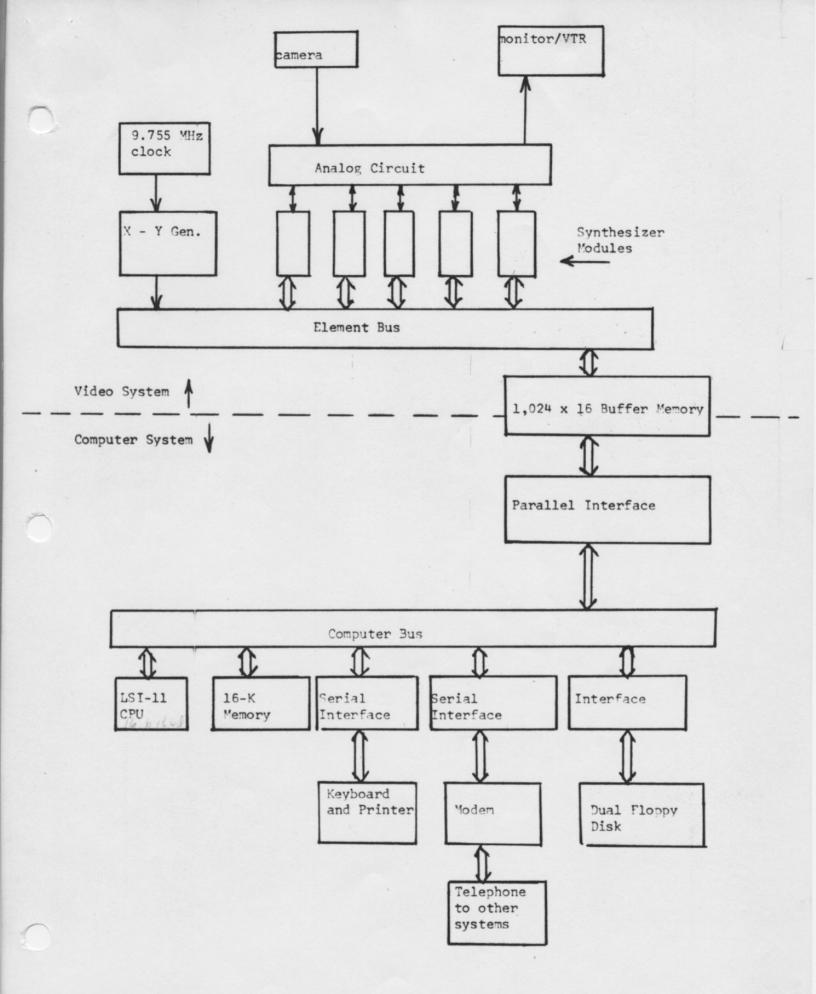

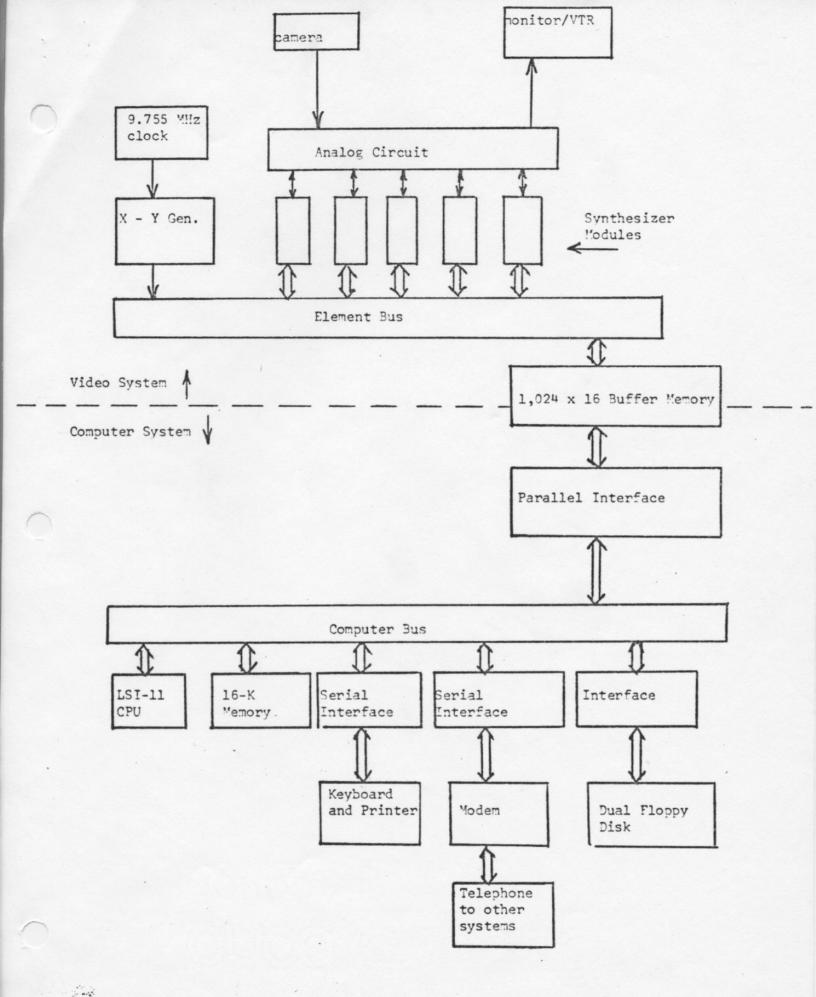

The computer-based video synthesizer system which is now operational at the Center consists of two sub-systems, the microprocessor and the video system and their interface. The computer section consists of a 16 bit DEC LSI-11 microprocessor, teletype and printer, dual floppy disk and 20K of memory. Components designed and constructed specifically for this project include the parallel interface, buffer memory, module to element bus, element bus, digital to analog

converters, analog to digital converters and real time input. The video system includes a four channel analog colorizer with keyers, a 50 point switching matrix, spatial and intensity digitizer and a voltage control bank. The video system is modular in design; each of these components was researched, designed and constructed over a period of four years under the research and development program at the Center. Each of the video components may be combined with any other to form a system tailored to individual requirements; the video system may be operated manually or placed under computer control. This design consideration allows a maximum flexibility with a limited amount of equipment, permitting the same components to serve a variety of artists with different systems needs and experiences. Hardware design also permits manual interruption of computer processes at any point through the use of analog to digital converters and real time input. This feature allows the artist more complete control over all elements of the image and its temporal structures. Changes in composition may occur by software reprogramming or direct manual interactions by the artist or a combination of these techniques.

A more detailed description of the hardware aspect of this project is presented in the papers by Dr. Donald McArthur. Section I A provides an orientation to the system architecture. Section I B is a paper written from a transcript of a presentation by McArthur in Buffalo, New York in March 1977 for the 'Design/ Electronic Arts' conference supported by the National Endowment for the Arts and the New York State Council on the Arts and sponsored by Media Study/Buffalo and the Center for Media Study, State University of New York at Buffalo. This presentation by McArthur was based directly on the research McArthur had done for the Computer-Based Video Synthesizer project.

The aim of the software aspect of the project was the development of an interactive language which uses concepts and vocabulary derived from the visual arts. It was anticipated that this approach would make the computer based video system accessible to a much larger number of artists than would a system which depends on the presence of a programmer to interpret the ideas and images of an artist into a computer language. Before any except the most rudimentary of programming could be developed, analysis of the fundamental elements in the composition of single images as well as their temporal structures had to be conducted. Identification and definition of these elements and the parameters of change within each variable were the initial steps. Within single images, discounting the time function, elements which were chosen included color field variables such as hue, saturation, chroma and intensity, form and shape variables including type of shape, position and frequency, texture and density. Each element has parameters of change which involve the temporal aspects of video. The methods of change involve problems of duration and sequencing with references to rhythmic structures.

As is noted in the papers by Wright, the software research is still in its initial stages and further explorations are necessary before the interactive language is fully functional. Several programs have been developed, one of which is analyzed in Wright's paper, section II A, which represents an incomplete stage of the

language. Section II B is a transcript of a presentation by Wright at the 'Design/ Electronic Arts' conference in Buffalo in 1977; these materials are based directly on the research Wright had done for this project.

The computer based video synthesizer system is now operational at the Experimental Television Center in Binghamton, New York and is available to artists under the production program. As a greater number of artists utilize this system, each artist will be encouraged to articulate ways in which the system can be made more responsive. The results of this project have already indicated several important avenues for continued research, among them further and continued software development and the publication and dissemination of the results of the research to date. The computer based video system can serve as a model system; publication of research results will allow the duplication and modification of the system by other individual artists and arts organizations. Although the research to date has been specific to video, microprocessor systems are useful tools in many of the visual and performing arts, and a publication of this nature would assist many individuals from a variety of fields. A complete set of documentation has already been prepared; the next phase of this project, for which the Center is seeking support, includes the publication of these materials, including detailed schematic documentation. This publication will also include more theoretical papers, approaching the system and its applications from the points of view of aesthetics, physics, electronics and video and microprocessor technology. The aim of this publication is to provide specific and detailed information to permit duplication of the system and also introduce conceptual frameworks from which to view the electronic arts.

EXPERIMENTAL TELEVISION CENTER LTD.

164 COURT ST.

BINGHAMTON NEW YORK 13901

607-723-9509

An Orientation to Hardware Architecture

Dr. Donald McArthur

Experimental Television Center Ltd. Binghamton, New York

July 1977

This project is supported in part by the National Endowment for the Arts and the New York State Council on the Arts.

# NEA Report

# I. Introduction

As science advances, with the resulting advances in technology, we have new tools and new capabilities which influence our world in many ways. This new technology not only influences the traditional art forms but also produces new forms of art. The development of high speed electronic components and circuits, the cathode ray tube, the video camera, and inexpensive video tape recorders enabled the development of video art. The development of small but powerful computers now allows systems to be developed which can give the video artist a new dimension of control over the video image. With a computer-based video synthesizer (CBVS), one can generate a sequence of images while controlling each individual image with detail and precision that is many orders of magnitude greater than is possible with manual control.

The ability to control the dynamics of the image is useful to the artist only if the system is capable of generating the image in real time. With this requirement in mind, the natural choice of devices for converting electrical signals to visual images is the conventional video system. This choice also gives the capability of recording the video compositions with a conventional video tape recorder and of broadcasting to a large audience through existing network systems.

There are basically two modes of operation of the system: interactive compositional mode and automatic production mode. In the compositional mode, the artist can enter programs and parameters through the keyboard, observe the resulting sequence of images, and then modify parameters through either the keyboard or a real time input and thus build up a data set for a complete piece. At each stage of the composition process the data set, representing all the aesthetic decisions made by the artist, is stored in the computer. When the composition is finished the system will operate in the automatic production mode generating the final video signal in real time with no intervention by the artist. The artist may also choose to use a combination of these two modes in an interactive performance or allow an audience to interact with the system operating automatically. The system is structured so that all of these variations can be accommodated by appropriate programming.

The system may be operated as a generating synthesizer which produces a video signal entirely from internal signals or as a processing synthesizer which utilizes signals of external origin such as a video camera. Either of these two types of operations is carried out by a configuration of element modules, each of which performs a class of functions, with the specific function during one frame being determined by the control parameters received from the computer.

Since the computer functions only to generate the parameters which povern the behavior of the synthesizer modules, a video signal will be generated without operation of the computer. The system will simply repeat the frame until the parameters are changed. Thus the artist may choose to stop the computer in which case he is able to examine a single frame, or he may alter the program so that a given sequence is displayed very slowly or repeated very rapidly.

# II. System Structure

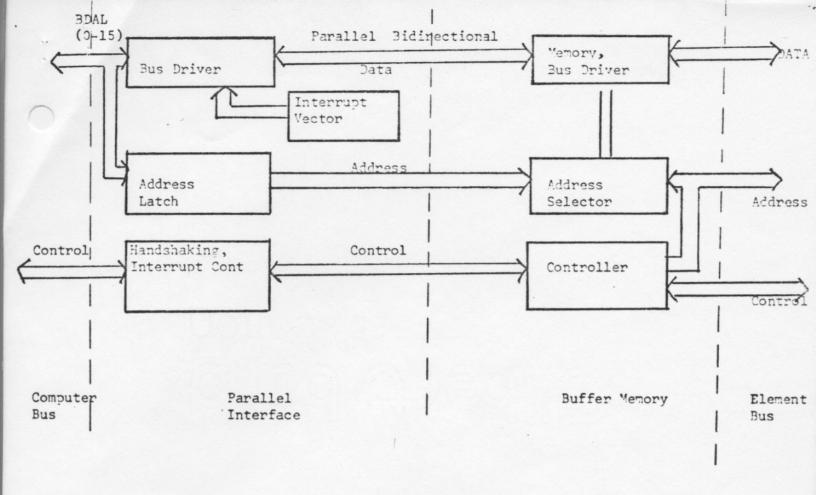

The CBVS consists of two parts: the computer section shown in the lower section of figure 1 and the video section shown in the upper section of the figure. Both sections operate simultaneously and independently, communicating through the buffer memory which has a capacity of 1,024 16 bit words. Each of these words is either a picture element, a number which controls some function of the video section and determines some aspect of one field of the video image, or it is a picture feature, a number determined by the video section and may depend on an external signal such as a video camera signal. The buffer memory is connected to the computer bus through a 16 bit parallel interface which is structured in such a way that each word in the buffer memory is addressable and may be read or written in exactly the same way as words in the main computer memory. This memory-mapped I/O system simplifies the software which controls the buffer memory. In order to update an element such as a control D/A, the computer must execute an instruction which stores the new value in the location corresponding to that element.

During the active scan time, the control computer reads features from the buffer memory and generates elements for the following field and stores them in the buffer memory. During the vertical blanking interval, information is transferred through the element bus from the buffer memory to the element modules or from the feature modules to the buffer memory. The designation of a particular area of the buffer memory as an element or feature is under program control. During the transfer between the buffer memory and the element bus, the computer is locked out of the buffer memory. On completion of the transfer, the interface generates a vectored interrupt which requests the computer to generate parameters for the next field.

The computer system consists of: a DEC LSI-11 microprocessor which has a 16 bit word length and an instruction execution time of about 7 microseconds; Teletype Keyboard and printer connected through a serial interface; 20 K of dynamic memory; a dual drive floppy disk system with a capacity of 256,256 bytes per diskette. An additional serial interface is also available for connecting through a modem to other computer systems. The entire system is dedicated to the synthesizer system.

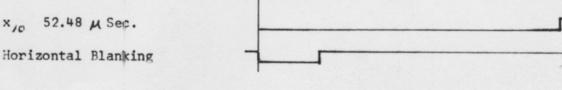

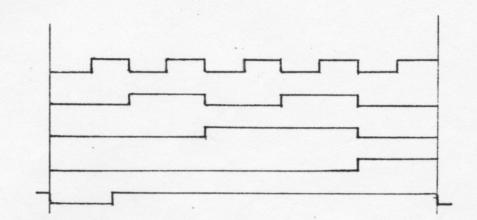

The overall timing is determined by a 9.7552434 MHz clock which is phase locked to the subcarrier (3.579545 MHz). This frequency is chosen to insure a coherent subcarrier and to divide the active portion of the scan line into 512 pixels. The red, green, and blue signals are generated independently, and the chroma encoding is done with analog circuits; thus there is no advantage to following the common practice of making the pixel rate an integer multiple of the subcarrier frequency. With this clock frequency, a full nine bit word is used to define the horizontal position on the active portion of the raster. Figure 2 shows the X and Y wave forms. The X-Y module generates twenty bits of timing information (ten bits for horizontal, including the blanking period, and ten for the line count). This module also generates sync, drive, burst flag, and the transfer request TR signal which controls the timing of the buffer memory.

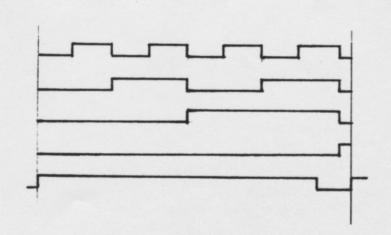

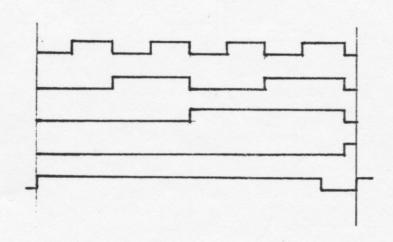

# NEA Report

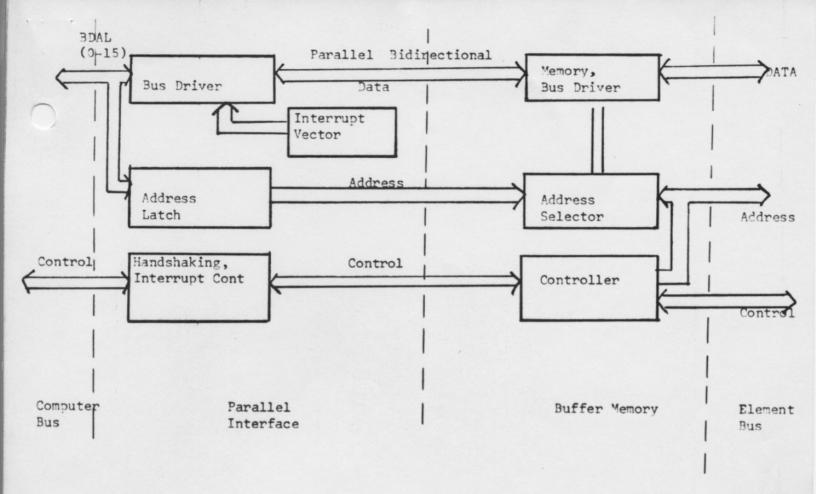

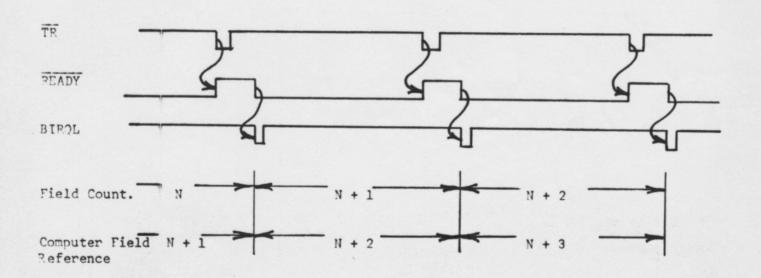

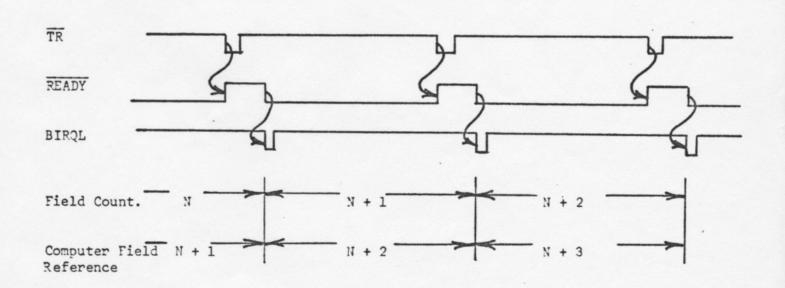

Timing details of the interface and buffer memory are shown in figure 3. The transfer request TR goes low at the beginning of vertical blanking initiating an arbitration for access to the buffer memory. If the computer is accessing the buffer memory, the current bus cycle is completed, then PEADY goes high, and the buffer memory controller cycles through memory making the required element and feature transfers. When this is completed, READY goes low, control of the memory is returned to the computer, and an interrupt is generated requesting data for the following field. As indicated in the diagram, during the Nth field, the computer is generating data for the N+lth field.

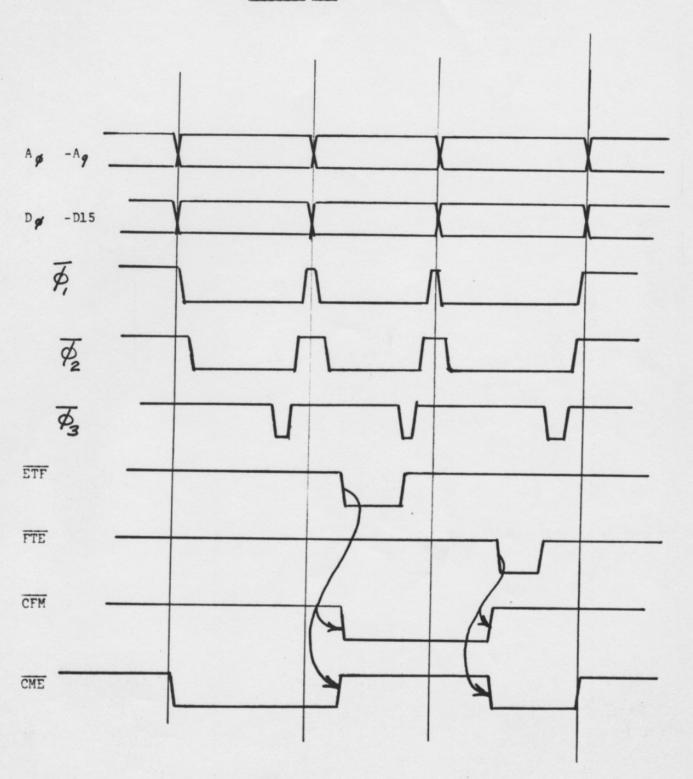

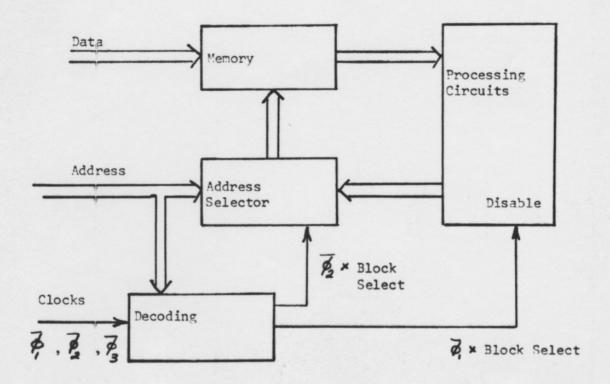

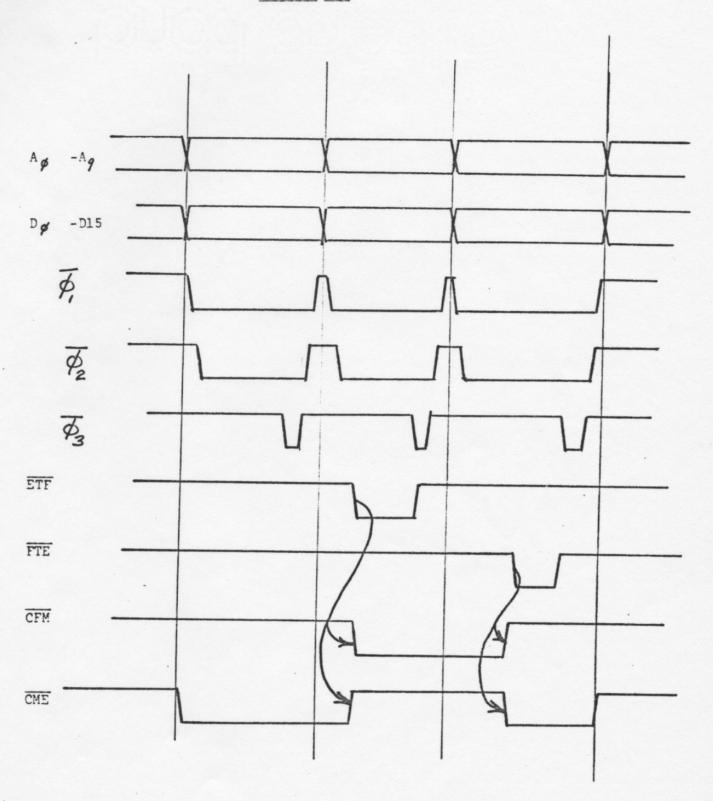

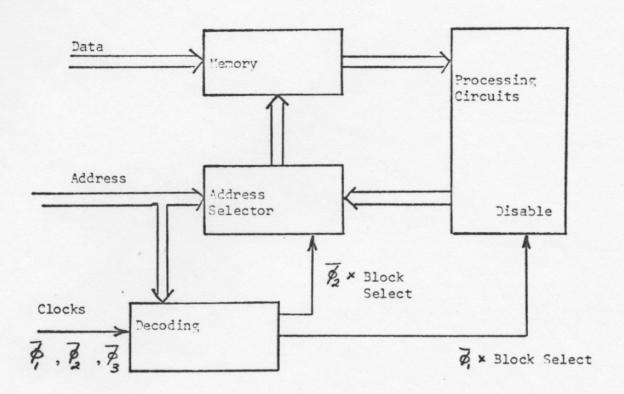

The timings of the signals on the element bus are indicated in figure 4. During the transfer, the memory controller generates: the addresses A -Aq ; the clock signals P, , Pq, and Pq; and the status signals CME indicating a transfer from the memory to an element and CFM indicating a transfer from a feature module to the memory. The signals ETF and FTE are generated by the synthesizer modules and initiate a controller Element/ Feature mode change. The three phase clock system is used to control modules which have the structure shown in figure 5. Functions which use data from the computer during the vertical blanking interval are disabled when the buffer memory accesses that particular element by a signal generated using

$\phi_{i}$  . This allows access to the buffer memory during  $\phi_{i}$  . The third clock,

\$\overline{\rho}\_3\$ generates a memory write signal.

Time delays in the digital processing modules could produce errors and shifts of the image to the right. This is prevented by deskewing the output of each with a latch clocked by the master clock (9.755 MHz.). Compensation for the resulting 102.5 nSec. delay in each module is provided by starting the X count at the beginning of the horizontal blanking interval rather than at the end. An additional shift to the right or left is then achieved by adding (mod 512) a constant supplied by the computer. The default value of this constant is 404 + number of elements.

# III. Element and Feature Modules

The structure described above supports a variety of element and feature modules which may be chosen and configured according to the tastes of the artist. Our experience indicates that a large amount of work can be produced with a relatively small number of elements in a standard configuration. Whenever possible, a new element added to the system is configured in such a way that if the control word is set equal to zero it has no effect on the system. Thus a minimum amount of reprogramming is required following system expansion.

Two general classes of modules have been developed: digital and hybrid. The hybrid elements are: high-speed D/A converters used for generating the red, green, and blue video signals which are converted to NTSC format in the standard wav; low-speed D/A converters used for generating control voltages, field-by-field controllable, used to operate existing voltage controlled analog image processing systems such as keyers, raster manipulaters, etc. Another hybrid element is the analog video switching matrix. Four bits of one control word are used to select one of sixteen inputs for one output.

Digital processing elements include: constant; X + constant; Y + constant; twelve-channel sixteen-line demultiplexer with output complement; and four-channel four-bit by sixty-four word memory.

# X and Y Half Cycle Durations and Wave Forms

- 102.5 nSec. x,

- 205 nSec. ×2

- ×3 410 nSec.

- 820 nSec. X4

- 1.64 A Sec. ×5

- 3.28 MSec. ×L

- 6.56 M Sec. × 7

- 13.12 A Sec. xx

- xq 26.24 A Sec.

Field Index

- У, 16.66 mSec.

- 63.5 µ Sec. y2

- 127 µ Sec. y 3

- 254 µ Sec. y4

- 508 MSec. V 5

- y L 1.01 mSec.

- 2.03 mSec. y,

- 4.06 mSec. y<sub>8</sub>

- 8.13 mSec. yg

- 16.26 mSec. y,0

Vertical Blanking

Figure 2

Figure 3

Figure 4

Figure 5

. . . .

EXPERIMENTAL TELEVISION CENTER LTD.

164 COURT ST.

PINGHAMTON NEW YORK 13901

607-723-9509

A Computer-Based Video Synthesizer System

A paper presented at the 'Design/Electronic Arts' conference in March 1977.

Dr. Donald McArthur

Experimental Television Center Ltd. Binghamton, New York

This project is supported in part by the National Endowment for the Arts and the New York State Council on the Arts.

# I. Introduction

As science advances, with the resulting advances in technology, we have new tools and new capabilities which influence our world in many ways. This new technology not only influences the traditional art forms but also produces new forms of art. The development of high speed electronic components and circuits, the cathode ray tube, the video camera, and inexpensive video tape recorders enabled the development of video art. Advances in integrated circuit design and fabrication techniques have led to the development of small but powerful computer systems which can be utilized by the video artist to achieve a new dimension of control over the video image. With a computer-based video synthesizer (CBVS), one can generate a sequence of images while controlling each individual image with detail and precision that is many orders of magnitude greater than is possible with manual control.

The ability to control the dynamics of the image is especially useful to the artist if the system is capable of generating the image in real time. With this requirement in mind, the natural choice of devices for converting electrical signals to visual images is the conventional video system. This choice also gives the capability of recording the video compositions with a conventional video tape recorder and of broadcasting to a large audience through existing network systems.

There are basically two modes of operation of the system: interactive-compositional mode and automatic-production mode. In the compositional mode, the artist can enter programs and parameters through the keyboard, observe the resulting sequence of images, and then modify parameters through either the keyboard or a real time input and thus build up a data set for a complete piece. The data set, representing all the aesthetic decisions made by the artist, is stored in the computer at each stage of the composition. When the composition is finished the system will operate in the automatic-production mode generating the final video signal in real time with no intervention by the artist. The artist may also choose to use a combination of these two modes in an interactive performance or to allow an audience to interact with the system operating automatically. The system is structured so that all of these variations can be accommodated by appropriate programming.

The system may be operated as a <u>generating synthesizer</u> which produces a video signal entirely from internal signals or as a <u>processing synthesizer</u> which utilizes video signals of external origin such as a camera. Either of these two types of operations is carried out by a configuration of elements modules, each of which performs a class of functions, with the specific function during one frame being determined by the control parameters recieved from the computer.

Since the computer functions only to generate the parameters which govern the behavior of the synthesizer modules, a video signal will be generated without operation of the computer. If the computer is stopped, the system will simply repeat the current frame until the parameters are changed. Thus the artist may choose to stop the computer and examine a single frame, or he may alter the program so that a given sequence is displayed very slowly or repeated very rapidly.

# II. General Design Considerations

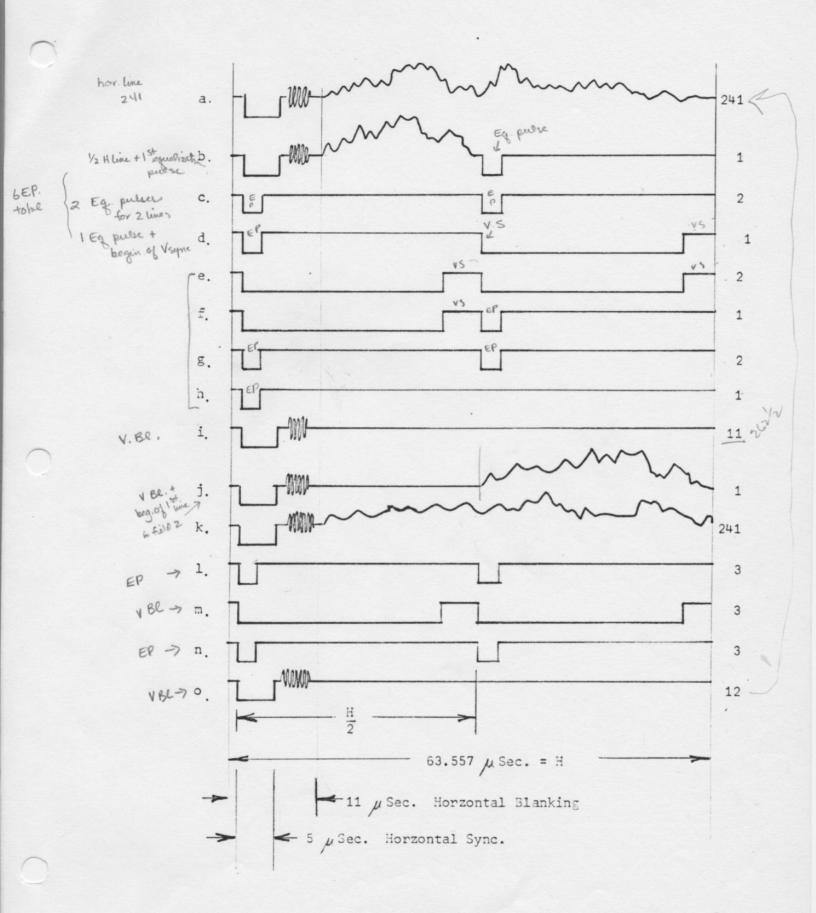

The NTSC video format is shown in figure 1. The time interval represented by one line is the time of one horizontal sweep or 1/15,734 sec. = 63.5 microseconds. The number by each line indicates the number of times that each format is repeated. There are 483 active scan lines and forty-two lines of vertical blanking making a total of 525 lines to compose one frame (two fields). The first line (a) consists of the horizontal sync pulse, which is five microseconds long occuring during a 11 microsecond blanking interval, followed by color burst and the picture information which last 52.6 microseconds. The next line (b) shows the first equalization pulse which is followed by five more and the beginning of vertical sync (lines c,d). Vertical sync starts in the middle of the line for this field and at the beginning of the line for the next field (line m). Lines e,f,g, and h show the completion of vertical sync with serrations and six more equalization pulses. Vertical blanking is shown in lines i and j. The second field starts in line j. Line k shows the 241 lines which interlace with the first field to complete the frame. Finally there are 6 more equalization pulses before (line 1) and after (line n) vertical blanking (line m). Line o shows twelve more lines of vertical blanking. This sequence is repeated 30 times per second making a total of 108,000 frames per hour.

The portion of the video signal which carries intensity information is a continuously varying voltage and may be analyzed into components of different frequencies: low frequency components correspond to course structures in the image, and high frequency components correspond to fine

structures. Although the video signal may, in general, have an arbitrary shape, a monitor will reproduce an image which corresponds to only a limited frequency range. This range is called the bandwidth. Thus components of the video signal which are outside the bandwidth of the monitor will not be visible. In a system any device which limits the bandwidth of the video signal will degrade the fine structure or spatial resolution of the image.

A video signal may be represented by a finite set of samples. These samples may be stored, eg. in a TBC or frame buffer, and then used to reproduce the video signal. In this process some of the information may be lost, but the lost information corresponds to high frequency components or fine structure of the image. If the sampling rate is sufficiently high, the lost information will be outside the bandwidth of the monitor, and no impairment of the image will occur. The minimum theoretical sampling rate which will retain the video information within a given bandwidth is called the Nyquist rate and is equal to twice the maximum frequency. Thus for broadcast quality, a minimum of 4.2 MHz. x 2 x 52 psec. = 437 samples per line are required.

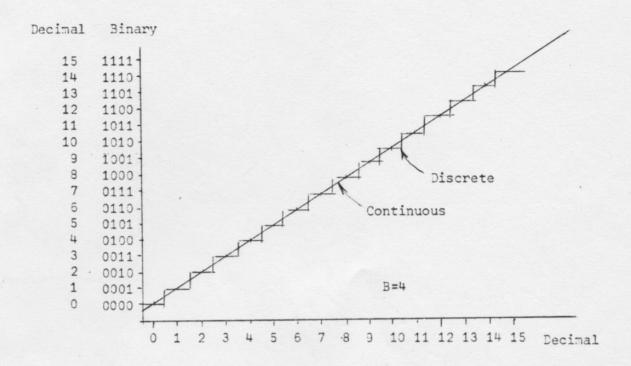

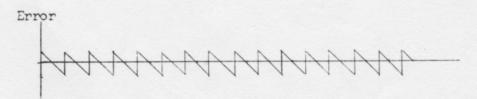

Each of the samples may be represented by a binary number with B digits.

B

In general, a binary number with B digits has 2 discrete values, and a B-digit representation corresponds to 2 discrete gray levels. Since the video signal may have any one of a continuous set of values, an error is introduced when it is represented by a discrete number. Figure 2 shows the correspondence between binary and decimal numbers, the correspondence between a continuous video signal and its discrete representation, and the resulting error. This error is called the quantization error, and its root-mean-square

value is given by

$$\sqrt{\int_0^1 \left(\frac{1}{2} \frac{1}{2^B} t\right)^2 dt} = \frac{1}{\sqrt{12}} \frac{1}{2^B}$$

.

If B is sufficiently large, the spacing between the discrete gray levels will be small compared to the intrinsic noise of the system and will not be visible on a monitor. The minimum acceptable value of B may be estimated by considering the quantization signal-to-noise ratio which is given by

sylvering the quantization signal-to-noise ratio which is

$$S/N = 20 \log \left\{ \sqrt{12} \quad 2 \right\} = (6.02 \text{ B} + 10.79) \text{ db.}$$

The signal-to-noise ratio for a one-half inch VTR is about 40 db, so about five binary digits are required for a comparable quality (monochrome) image.

For the analysis of equipment requirements for generating a video signal, we may utilize the measure of information given by the mathematical theory of communication. If a message occurs with probability P, then the amount of information (measured in bits) is

$$I = \log_{2} (1/P).$$

Thus, the answer to a question which can be answered by yes or no with equal probability carries the quantity of information of

$$\log_2 \frac{1}{(1/2)} = \log_2 2 = 1$$

bit,

Since a binary digit has two possible values, zero and one, each may carry at most one bit of information. Thus there are 5 x 437 x 483 = 1,055,355 bits of information in one frame of monochrome video signal (assuming thirty-two gray levels and 4.2 MHz. bandwidth). For generating a color signal, one may represent each of the red, green, and blue primary signals with a five bit word specified at time intervals of 100 nSec; this corresponds to an information rate of 150,000,000 bits per second. Other examples of amounts

of information are typewriter keystroke, about six bits, and one typewritten page (double spaced), 9,000 bits. The rate at which the human brain can process information has been estimated to be about forty bits per second.

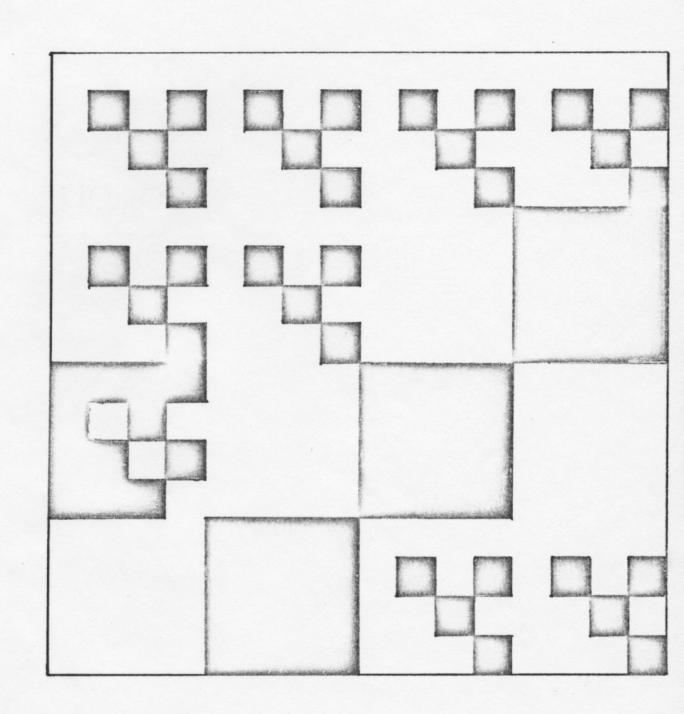

The mathematical theory of communication introduces another concept, redundancy, which is useful in analyzing a video synthesizer system. A message which contains N bits of information may be coded in a way that uses more than N binary digits. For example, the message pair (yes/no) may be coded as (111/000) using three binary digits instead of one per message. In this case the coding is redundant. The pattern shown in figure 3 consists of 16 x 16 = 256 squares, each of which is either all black or all white. Thus by representing white by one and black by zero, any pattern of this format can be represented by a code consisting of 256 binary digits. If all possible patterns are allowed, then one pattern carries 256 bits of information. A circuit which generates a video signal corresponding to this pattern codes the message into a form with 1,055,355 binary digits (assuming the spatial and intensity resolution as above). The redundancy of the video signal is further increased if the set of possible patterns is restricted by requiring that the total pattern is built of sixteen 4 x 4 blocks each being one of the following: all black, all white, black and white as in the upper left hand corner, or the latter with black and white interchanged. Then two binary digits code the choice for each block, and since there are sixteen blocks, thirty-two bits of information are contained in the entire pattern.

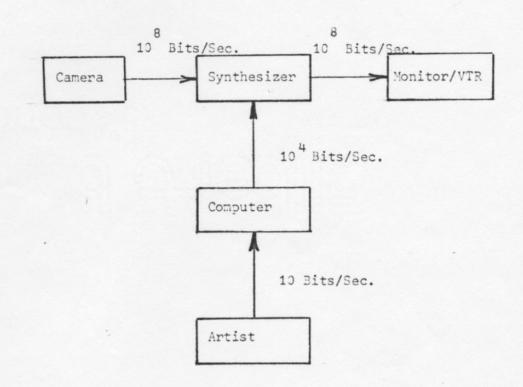

The disparity between the rate at which the human brain can process information, which limits the rate that an artist can manipulate controls of a video synthesizer, and the rate that information must be generated in

be structured in such a way to exploit redundancy in the video signal. A microprocessor typically requires 2 to 10 µSec. to execute a single instruction; thus it cannot possibly be used to generate a point every 100 nS as required for a video signal in real time. On the other hand, one video field last 1/60 = 16.67 mS., a duration in which several thousand instructions can be executed. Thus a microprocessor is capable of generating signals according to a complex algorithm—utilizing information supplied by the artist to produce control signals for high-speed special-purpose devices at a field-by-field rate.

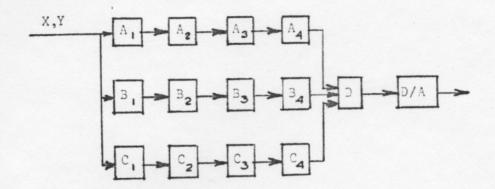

Thus we are led to the hierarchical structure shown in Figure 4.

Typical channel capacities are shown for each interconnection. The synthesizer consists of high speed special purpose circuits which generate a video signal with a character determined by the control signals supplied by the computer. The control signals fix the behavior of these circuits for an entire field. The computer takes information supplied by the artist, information defining the composition as a whole, and from it determines the control parameters required by the synthesizer for each field. Thus a gradual change in some picture parameters can be specified by the artist by a small set of numbers. In the simplest case only two numbers are required, the frame count of the first and last frame of the sequence. The computer utilizes this information to calculate the corresponding picture parameters for each field; thus it may produce several thousand control values.

# III. System Structure

The CBVS consists of two parts: the computer section shown in the lower section of figure 5 and the video section shown in the upper section of the figure. Both sections operate simultaneously and independently, communicating through the buffer memory which has a capacity of 1,024 sixteen-bit words. Each of these words is either a picture element, a number which controls some function of the video section and determines some aspect of one field of the video image, or it is a picture feature, a number determined by the video section and may depend on an external signal such as a video camera signal. The buffer memory is connected to the computer bus through a sixteen-bit parallel interface which is structured in such a way that each word in the buffer memory is addressable and may be read or written in exactly the same way as words in the main computer memory. This memory-mapped I/O system simplifies the software which controls the buffer memory. In order to update an element such as a control D/A, the computer must execute an instruction which stores the new value in the location corresponding to that element.

During the active scan time, the control computer reads features from the buffer memory and generates elements for the following field and stores them in the buffer memory. During the vertical blanking interval, information is transferred through the element bus from the buffer memory to the element modules or from the feature modules to the buffer memory. The designation of a particular area of the buffer memory as an element or feature is under program control. During the transfer between the

buffer memory and the element bus, the computer is locked out of the buffer memory. On completion of the transfer, the interface generates a vectored interrupt which requests the computer to generate parameters for the next field.

The computer system consists of a DEC LSI-11 microprocessor which has a sixteen-bit word length and an instruction execution time of about 7 microseconds, a Teletype Keyboard and printer connected through a serial interface, 20 K of dynamic memory, and a dual floppy disk system with a capacity of 256,256 bytes per diskette. An additional serial interface is also available for connecting through a modem to other computer systems. The entire system is dedicated to the synthesizer system.

The overall timing is determined by a 9.7552434 MHz clock which is phase locked to the subcarrier (3.579545 MHz). This frequency is chosen to insure a coherent subcarrier and to divide the active portion of the scan line into 512 pixels. The red, green, and blue signals are generated independently, and the chroma encoding is done with analog circuits; thus there is no advantage to following the common practice of making the pixel rate an integer multiple of the subcarrier frequency. With this clock frequency, a full nine bit word is used to define the horizontal position on the active portion of the raster. Figure 6 shows the X and Y wave forms. The X-Y module generates twenty bits of timing information (ten bits for horizontal, including the blanking period, and ten for the line count). This module also generates sync, drive, burst flag, and the transfer request TR signal which controls the timing of the buffer memory.

Timing details of the interface and buffer memory are shown in figure

7. The transfer request  $\overline{TR}$  goes low at the beginning of vertical blanking initiating an arbitration for access to the buffer memory. If the computer is accessing the buffer memory, the current bus cycle is completed, then  $\overline{READY}$  goes high, and the buffer memory controller cycles through memory making the required element and feature transfers through the element bus. When this is completed,  $\overline{READY}$  goes low, control of the memory is returned to the computer, and an interrupt is generated requesting data for the following field. As indicated in the diagram, during the Nth field the computer is generating data for the N+1th field.

The timings of the signals on the element bus are indicated in figure 8. During the transfer, the memory controller generates—the addresses,  $A\phi$ -Aq, the clock signals  $\phi$ ,  $\phi$ , and  $\phi$ , and the status signals  $\overline{\text{CME}}$  indicating a transfer from the memory to an element and  $\overline{\text{CFM}}$  indicating a transfer from a feature module to the memory. The signals  $\overline{\text{ETF}}$  and  $\overline{\text{FTE}}$  are generated by the synthesizer modules and initiate a controller Element/ Feature mode change. The three phase clock system is used to control modules which have the structure shown in figure 9. Functions which use data from the computer during the vertical blanking interval are disabled when the buffer memory accesses that particular element by a signal generated using  $\overline{\phi}$ . This allows access to the buffer memory during  $\overline{\phi}$ . The third clock  $\overline{\phi}$  generates a memory write signal.

Time delays in the digital processing modules could produce errors and shifts of the image to the right. This is prevented by deskewing the output of each with a latch clocked by the master clock (9.755 MHz).

Compensation for the resulting 102.5 nSec. delay in each module is provided

by starting the X count at the beginning of the horizontal blanking interval rather than at the end. An additional shift to the right or left is then achieved by adding (mod 512) a constant supplied by the computer. The default value of this constant is 404 + number of elements.

# IV. Element and Feature Modules

The structure described above supports a variety of element and feature modules which may be chosen and configured according to the taste of the artist. Our experience indicates that a large amount of work can be produced with a relatively small number of elements in a standard configuration. Whenever possible a new element added to the system is configured in such a way that if the control word is set equal to zero it has no effect on the system. Thus a minimum amount of reprogramming is required following system expansion.

Two general classes of modules have been developed, digital and hybrid.

The hybrid elements are high-speed digital-to-analog converters used for generating the red, green, and blue video signals which are converted to NTSC format in the standard way and low-speed D/A converters used for generating control voltages, field-by-field controllable, used to operate existing voltage-controlled analog image processing systems such as keyers, raster manipulaters, etc. Another hybrid element is the analog video switching matrix. Four bits of one control word are used to select one of sixteen inputs for one output.

Digital processing elements include: constant, X + constant, Y + constant, twelve-channel sixteen-line demultiplexer with output complement, and four-channel four-bit by sixty-four word memory.

One of the possible ways of interconnecting digital element modules is shown schemetically in figure 10. With this arrangement the X and Y signals are processed by the three sequences  $(A,A_2A_3A_4)$ ,  $(B_1B_2B_3B_4)$ ,

and (C<sub>1</sub>C<sub>2</sub>C<sub>3</sub>C<sub>4</sub>) to produce three different patterns or textures. These three signals are then combined by element D to produce a composite image. Finally, the digital-to-analog converter produces an analog video signal. The form of the video signal generated by this system depends on both the choice of configuration of modules and on the control parameters supplied by the computer. Since the control parameters are constant during one frame, the video signal may be represented by an equation of the form

$$V(t) = f[X(t), Y(t), E_1(t), \dots E_n(t)]$$

where V(t) is the video signal which varies with time t. The structure of V(t) and of the resulting image is determined by the function f which is defined by the configuration of element modules. The time dependence of the video signal is shown explicitly; during one field, only X and Y change while the control values  $E_1(t)$ ,  $E_2(t)$ ,  $E_3(t)$ ,.... $E_n(t)$  are held constant. The time dependence of the video signal has been divided into two classes: firstly, the variation from one field and the next is determined by the computer through the element values, and secondly, the variation during one field is determined by the element modules through the X and Y signals for fixed element values.

# V. System Operation

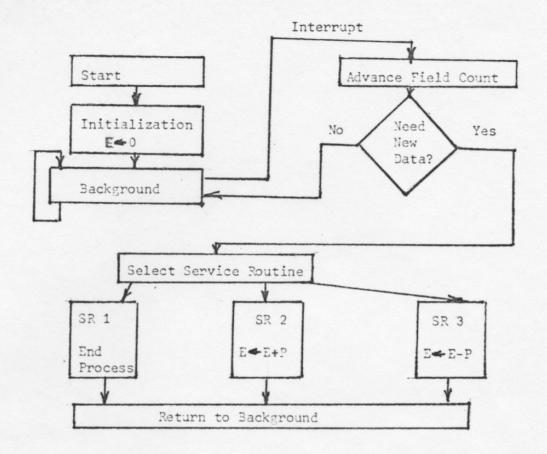

The power and versatility of this system may be seen by considering an application to an extremely simplified version of the system consisting of a pair of camera signals which are mixed by a voltage controlled mixer. With this system, only one element, a low-speed digital-to-analog converter, utilizes the element bus, and it generates a control voltage which determines the mixer operation for each frame. A flow chart of a program and an example of a data set are shown in figure 11. To use this system, the artist only needs to specify the numerical values in the data set.

The data set in this example corresponds to the mixer selecting the first camera until frame number 600, then fading to the second camera until frame 700, holding the second camera until frame 2000, then fading back to the first camera by frame number 2200. The values 8 and 4 in the parameter column determine the rate at which the fade takes place, and the numbers in the service routine column label indicate the selected service routine: a 1 for no change, a 2 for increasing the control voltage by P units, and a 3 for decreasing the control voltage by P units.

After the artist has stored these twelve numbers in the computer memory, the program may be started, and the computer will initialize the system and go to a background program where it waits for an interrupt. After every other interrupt the frame count is increased by one and compared with the frame count entry in the data set. Then the appropriate service routine (SR) is selected, and the element value is increased or decreased as required. Finally, the computer returns to the background

program and waits for the next interrupt. This process is repeated for every field thus generating the sequence of control voltages and fading from one camera to the other.

The artist can observe the resulting sequence of images and then make changes in the data set to achieve the desired result. This technique may be extended to more complex systems involving several elements and feature modules with corresponding programs and data sets. Thus the artist can produce complex sequences with precise control of each frame. When the composition is finished, the system will automatically generate the video signal which may be displayed on a monitor or recorded on a VTR.

Figure 5

# X and Y Half Cycle Durations and Wave Forms

- x, 102.5 nSec.

- x, 205 nSec.

- ×3 410 nSec.

- x4 820 nSec.

- x5 1.64 A Sec.

- x6 3.28 MSec.

- x7 6.56 µSec.

- xy 13.12 A Sec.

- xq 26.24 \$ Sec.

- x,0 52.48 M Sec.

- Horizontal Blanking

- Field Index

- y, 16.66 mSec.

- y2 63.5 µ Sec.

- уз 127 µ Sec.

- y4 254 µ Sec.

- y 5 508 MSec.

- y 6 1.01 mSec.

- y, 2.03 mSec.

- y<sub>8</sub> 4.06 mSec.

- y, 8.13 mSec.

- y,c 16.26 mSec.

Vertical Blanking

Data Set

| Frame count | Service<br>Routine<br>Lable | Parameter<br>P |

|-------------|-----------------------------|----------------|

| 600         | 2                           | . 8            |

| 700         | 1                           | 0              |

| 2000        | 3                           | 4              |

| 2200        | 1                           | 0              |

EXPERIMENTAL TELEVISION CENTER LTD.

164 COURT ST.

PINGHAMTON NEW YORK 13901

607-723-9509

A Computer-Based Video Synthesizer System

Software

Walter Wright

Experimental Television Center Ltd. Binghamton, New York

July 1977

This project is supported in part by the National Endowment for the Arts and the New York State Council on the Arts.

EXPERIMENTAL TELEVISION CENTER LTD.

164 COURT ST.

PINGHAMTON NEW YORK 13901

607-723-9509

A Computer-Based Video Synthesizer System

Software

Walter Wright

Experimental Television Center Ltd. Binghamton, New York

July 1977

This project is supported in part by the National Endowment for the Arts and the New York State Council on the Arts.

The first program was developed for Woody Vasulka who uses an LSI-11 microcomputer interfaced to video synthesis modules including digital to analog converters, (D/A's), analog to digital converters (A/D's), Don McArthur's modules described elsewhere in this report and George Brown's multiple level keyer.

The D/A's and A/D's are controlled through four words in memory as follows:

- L. status word LEWSTA at location 167770

- 2. output word LEWOUT at location 167772

- 3. input word LEWIN at location 167774

- 4. channel address LEWCHA at location 167776

McArthur's modules are controlled through the buffer memory which appears as normal memory to the program. Any location in buffer memory can be read in or written to, and finally arithmetic and logic operations can be performed thereupon. This technique of "memory-mapped I/O" makes the programmer's life much easier and besides it's quick - important because all modules must be updated in less than 1/60 sed. Control words for McArthur's modules are located in the upper reaches of memory as follows.

Next the system macros are invoked with the following statements: BEGIN: .MCALL .. V2.., . REGDEF, . EXIT

. REGDES

.. V2..

The label BEGIN: is used by the linking loader to identify the entry point for the main program. This is done using this statement at the end of the program:

.END BEGIN

The .. V2.. macro identifies the monitor system being used by the LSI-11. The .REGDEF macro defines the LSI-11's internal registers using two character mnemonics as follows -

- 10 RO general purpose register 0

- 2) Rl general purpose register 1

- 3) R2 general purpose register 2

- 4) R3 general purpose register 3

- 5) R4 general purpose register 4

- 6) R5 general purpose register 5

- 7) PC program counter, register & g caate of next mishvolim to be executed

8) SP stack pointer, register & location of last entry on stack

Now we're ready to initialize the D/A's which is accomplished thus -

1) VOM #100000, @# LEWOUT

2) MOV #10,R0

3) BGNI: DEC RO

| 4) | MOV | RO, @# LEWCHAZ |

|----|-----|----------------|

| 5) | TST | RO             |

| 6) | BNE | BGM            |

The first line of code mawes the octal number 100000 to the output word in memory which controls the D/A's. This causes the D/A to output a constant OV (+10Vv= 177700 & -10V = 0). The prefix # defines a real number, and the prefix @# defines an address (a location in memory). However the data transfer is not consummated until the D/A channel is addressed through the channel address word. The are 8 D/A channels 0 - 7. Therefore we set register 0 to the octal number 10 = decimal 8 (line 2). Then we count down register 0 with a loop (lines 3,5 & 6) and at the same time enable the D/A's by moving the contents of register 0 to the channel address word (line 4).

And we initialize the buffer memory -

| 1) | MOV | #DONOUT_, RO  |

|----|-----|---------------|

| 2) | CLR | (RO) +        |

| 3) | CLR | (RO) +        |

| 4) | CLR | (RO) +        |

| 5) | CLR | (RO) +        |

| 6) | MOV | # JEFOUT , RO |

| 7) | CLR | (RO) +        |

| 8) | CLR | (RO) +        |

| 9) | CLR | (RO) +        |

This code uses the auto-increment mode of addressing (register) +.

Line 1 moves the octal number 171040 into register 0. Then we clear that

memory location and add \* 2 to register 0 which now points to the next

word in memory (lines 2-5). This sets the red, green and blue 16%1 select

channels to black and the inversion register to normal (non-inverting).

Similiarly the ALU's are set to pass red, green and blue respectively.

The maximum number of data buffers is set -

MOVB #20 , TMRY

That is, the program tolerates no greater than octal 20 = 16 decimal buffers.

This fact is recorded in the byte labelled TMRY.

Each data buffer is associated with four parameter words and these 64 words (4x16) are kept in the parameter buffer PBUF. We initialize this buffer as follows -

| 1)       | MOV         | #PBUF , RO  |             | 42    | v v    |

|----------|-------------|-------------|-------------|-------|--------|

| 2)       | SUB         | #10 , RO    |             |       |        |

| 3) BGN2: | CMPB<br>BPL | TMRX , TMRY | # time thru | TIMEX | RO     |

| 5)       | INCB        | TMRX        | ) 7)        | 0     | 10040  |

| 6) 6     | ADD         | #10 , RO    | 7)          | 3     | 180,69 |

| 7) 8     | CLR         | (RO)        | 9           | 3     | 10075  |

| 8)       | MOV         | #1 , 2(RO)  |             |       |        |

| 9)       | MOVB        | TMRX , R1   |             | 15,   |        |

| 10) -    | DEC         | R1          |             | []    |        |

| 11) | SWAB | R1 |

|-----|------|----|

|     |      |    |

12) ADD #DBUF , R1

13) MOV R1 , 4 (R0)

14) CLR 6(R))

15) BR BGN2

16 PBUF: .= .+700

Again we use a loop; we set register 0 to the location of PBUF (lines 1 and 2). Note PBUF is effeated by causing the program counter (.) to skip over 64 words of memory (line 16). The loop is controlled by TMRX and T TMRY. TMRX counts up to the maximum number of data buffers, then a branch to the next block of code is executed (lines 3,4,5 and 15). The four parameterswords are -

| 1) | timing counter  | RØ    |

|----|-----------------|-------|

|    |                 | 2(RØ) |

| 2) | timing interval | 4(RØ) |

| 3) | pointer to DBUF | 6(RØ) |

4) data

The first word is cleared (line 7). The timing interval is set to a single field (line 8). Next address of the data buffer is calculated and put in the third word (lines 9-13). There are 16 data buffers each containing 128 words. Therefore the pointer is set initially as follows -

pointer = #DBUF + (256 \* (TMRX - 1))

This formula is coded from right to left.

In line 9 TMRX is moved into register 1/ the decrement instruction in line 10 subtracts 1 from the register; the weap byte instruction in line 11 effectively multiplies the register by 256 (equivalent to 8 left shifts or multiplication by 2 ); DBUF is added to register in line 12; and finally in line 13 the result is stored in the parameter buffer using the indexed addressing mode (6(90) the contents of register 0 plus the index 6 produce the effective address).

From here we go to the timing routine (TMR). This routine enables the 1/60 sec interrupt, and every 1/60 sec polls the parameter buffer checking for time outs (timing counter equal timing interval). If a data buffer times out a branch to the next block of code is executed.

The buffer memory transfers data to the modules during the vertical interval between each field of video. Then the buffer memory generates an interrupt telling the computer to get working on data for the next field. This interrupt is enabled or disabled with the status word (G#DONSTA). If the status word equals 1 the interrupt is enabled; if 0 the interrupt is disabled. So much for the buffer memory - the LSI - 11 handles interrupts thus. The computer interrupts its normal flow of operations and as a precaution pushes the current program counter (PC or register 6) and the program status word (PSW) onto the stack. The stack pointer (SP) is decremented by 4. Then the computer goes to a predeter-

mined location in memory (in this case @# 170) and uses the contents of this location as the new program counter (PC). Execution begins anew from the location pointed to by @# 170. Usually this is an interrupt service routine, however I have taken a shortcut as explained below.

- 1) 1) TMR: MOV #TMRI , 0# LEO

- 2) CLRB TMRX

- 3) INC @# DONSTA

- 4) BR

- 5) TMRI: CLR @# DONSTA

- 6) ADD 4, SP

In line 1 we prepare for the inevitable interrupt by loading location 170 with the location #TMRI; the location where we will resume execution.

Next the fuffer counter (TMRX) is cleared and the interrupt is enabled (Lines 2 and 3). Now we wait for the interrupt by executing the branch instruction on line 4. Following the interrupt we return to line 5 and disable further interrupts by clearing the status word in the buffer memory. Then in line 6 we do some housekeeping, restoring the stack pointer (SP).

We are now ready to poll the data buffers -

1) MOV #PBUF , R-0

| 2)  |       | SUB   | #10 , RO    |

|-----|-------|-------|-------------|

| 3)  | TMRZ: | CMPB  | TMRX , TMRY |

| 4)  |       | BPL   | TMR         |

| 5)  |       | INCB  | TMRX        |

| 6)  |       | ADD   | #10 , RO    |

| 7)  |       | MOVB  | TMRX , R 2  |

| 8)  |       | DEC   | R2          |

| 9)  |       | ADD   | #EBUF , R2  |

| 10) |       | TSTB  | (R2)        |

| 11) |       | BEQ   | TMR2        |

| 12) |       | INC   | (RO)        |

| 13) |       | CMP   | (RØ)        |

| 14) |       | BLE   | TMR2        |

| 15) | TMR3: | CLR   | (RO)        |

| 16) |       | JSR   | PC , INT    |

| 17) |       | BR    | TMR2        |

| 18) | TMRX: | .BYTE | 0           |

| 19) | TMRY: | BYTE  | 0           |

|     |       |       |             |

Again we have a loop similiar to the loop used to initialize the parameter buffer. Lines 1 and 2 lead register 0 with #PBUF - 8. In line 3 the counter (TMRX initially 0) and the number of buffers (TMRY) are compared. Assuming all the buffers were checked we branch back to wait for

the next interrupt (line 4). Otherwise we increment register 0 by 8 (line 6) and check the enable buffer (lines 7 to 10). If the buffer is disabled (the contents of location #EBUF + (TMRX - 1) equal 0) we branch back to TMR2 (line 11). If the buffer is enabled the timing counter is incremented (line 12) and compared with the timing interval (line 13). If the counter is less than or equal the interval we branch back to TMR2 (line 14).OtOtherwise we clear the timing counter and jump to the interpreter routine (lines 15 and 16). Upon returning from the interpreter, (line 17), we branch back to TMR2 completing the timing routine. Lines 18 and 19 reserve space im memory for the buffer counter (TMRX) and the number of buffers (TMRY).

#### NEA - DEVELOPMENT PROGRAM

The interpreter reads a command word from the data buffer and uses this word to create a special jump subroutine instruction. The subroutine in turn executes the command reading additional data words from the buffer as required.

| 1)  | INT:  | MOV | 4(RO) , R1  |

|-----|-------|-----|-------------|

| 2)  |       | MOV | (R1)+ , R2  |

| 3)  |       | ASL | R2          |

| 4)  |       | ADD | #JBUF , R2  |

| 5)  |       | MOV | (R2) , R2   |

| 6)  |       | SUB | #INTI , R2  |

| 7)  |       | MOV | R2 , INTI-2 |

| 8)  |       | CLR | R5          |

| 9)  |       | JSR | PC , EXIT   |

| 10) | INTI: | MOV | R1 , 4(R0)  |

| 11) |       | TST | R5          |

| 12) |       | BEQ | INT         |

| 13) |       | RTS | PC          |

Remember that register 0 contains the address of the first of the four parameter words controlling the data buffer. In line 1 the data pointer (4(RO)) is moved to register 1. Then the command word ((R1)+) is moved from the data buffer to register 2; and the data pointer in auto-incremented

(line 2). The jump subroutine through the program counter instruction (line 9) is decoded by the assembler as two words - 004767, XXXXXX. The first three digits of the first word (004) indicate a JSR instruction. The fourth digit (7) indicates that register 7 (PC) will be the linkage pointer. The fifth and sixth digit represent the destination, the fifth digit specifies the index addressing mode and the sixth digit indicates that the index value follows the instruction. The index value plus the program counter equals the destination address. In lines 3 - 6 the index value is calculated using these formulae -

- 1) index = subroutine entry pt # INTI

- 2) subroutine entry pt = # JBUF + (2 \*Command word)

The index value is moved to location INTI 2 (line 7). Register 5 is a done flag set following the output command, it is cleared initially (line 8). The jump subroutine instruction is executed (line 9), the program executes the appropriate subroutine, and returns to restore the data buffer pointer (line 10). The done flag (R5) is tested (line 11); if zero the program branches back and reads the next command word (line 12), or returns to the timing routine (line 13).

A cross reference table (JBUF) follows the interpreter. The entry points for the subroutines are stored sequentially and are accessed with the command word. A summary of the function of each subroutine follows -

SUB00 - (00) sets the timing interval (second word in the parameter list) equal to the next word in the data buffer.

MOV (R1) + , 2 (R0)

SUB01 - (01) adds the next word in the data buffer to the timing interval.

ADD (R1) + , 2 (R0)

SUB02 - (02) subtracts the next word in the data buffer from the timing interval.

SUB (R1) + , 2(R0)

SUB03 - (03) complements the timing interval, equivalent to 177777 - 8

COM 2(RO)

SUB04 - (04) shifts the timing interval to the right, the most significant bit (bit 15) is cleared, equivalent to timing interval/2.

CLR

ROR 2 (RO)

SUB05 - (05) shifts the timing interval to the left, the least significant bit (bit 0) is cleared, equivalent to 2\* timing interval.

CLR

ROL 2 (RO)

Command words 06 and 07 are not used, therefore they are cross referenced to the error routine ERR in JBUF.

SUB 10 - (10) sets the data word (fourth word in the parameter list) equal to the next word in the data buffer.

MOV (R1) +, 6 (R0)

SUB 11 - (11) increments the data word, equivalent to data word + 1.

INC 6(RO)

SUB 12 - (12) decrements the data word, equivalent to data word - 1.

DEC 6 (RO)

SUB 13 - (13) adds the next word in the data buffer to the data word.

ADD (R1) +, 6 (R0)

SUB 14 - (14) subtracts the next word in the data buffer to the data word.

SUB (R1) +, 6 (R0)

SUB 15 - (15) complements the data word, equivalent to 177777 - data word.

COM 6 (RO)

SUB 16 - (16) shifts the data word to the right, the most significant bit (bit 15) is cleared, equivalent to data word/2.

bit n becomes bit n-1

bit 0 dropped

CLC

ROR 6 (RO)

SUB 17 - (17) shifts the data word to the left, the least significant bit (bit 0) is cleared, equivalent to 2\* data word.

bit n becomes bit n+1

bit 15 dropped

CLC

ROL 6(RO)

SUB 20 - (20) rotates the data word to the right, shifts the bits right, the least significant bit (bit 0) is rotated around to become the most significant bit (bit 15).

15

-0

bit 0 becomes bit 15

MOV 6 (RO), R2

ROR R2

ROR 6 (RO)

SUB 21 - (21) rotates the data word to the left, shifts the bits left, the most significant bit (bit 15) is rotated around to become the most significant bit (bit 0).

15

0

bit 15 becomes bit 0

MOV 6 (RO), R2

ROL R2

ROL 6 (RO)

SUB 22 - (22) takes the next word in the data buffer and clears each bit in the data word which corresponds to a set bit in the former, equivalent to - data word = ~next word in buffer \( \) data word

eg. next word in buffer 0 000 001 010 011 100

data word 0 000 001 101 100 111

data word 0 000 000 101 100 011

BIC (R1) +, 6 (R0)

SUB 23 - (23) takes the next word in the data buffer and sets the corresponding bits in the data word, equivalent to - data word + next word in buffer V data word.

eg. next word in buffer 0 000 001 010 011 100

data word 0 000 001 001 001

data word 0 000 001 011 011 101

BIS (R1) +, 6 (R0)

SUB 24 - (24) takes the next word in the data buffer and exclusive OR's  $(\forall)$  it with the data word.

eg. next word in buffer 0 000 001 010 011 100

data word 0 000 001 001 001

data word 0 000 000 011 010 101

MOV (rl) +, R2

XOR R2 , 6 (R0)

Command words 25, 26 and 27 are not used, therefore they are cross-referenced to the error routine ERR in JBUF.

SUB 30 - (30) calls the input routine and sets the data word equal to input data (in register 2).

JSR PC , IN

MOV R2, 6 (R0)

SUB 30 - (30) calls the input routine and sets the data word equal to input data (in register 2).

JSR PC , IN

MOV R2, 6 (R0)

SUB 31 - (31) calls the input routine and adds the input data to the data word.

JSR PC , IN

ADD R2, 6 (RO)

SUB 32 - (32) calls the input routine and subtracts the input data from the data word.

JSR PC , IN

SUB R2 , 6 (R0)

SUB 33 - (33) calls the input routine and clears each bit in the data word as in SUB 22.

JSR PC , IN

BIC R2 , 6 (R0)

SUB 34 - (34) calls the input routine and sets each bit in the data word as in SUB 23.

JSR PC , IN

BIS R2 , 6 (R0)

SUB 35 - (35) calls the input routine and exclusive OR's the input data with the data word as in SUB 24.

JSR PC , IN

XOR R2 , 6 (R0)

Command words 36 and 37 are not used, therefore they are cross-referenced to the error routine ERR in JBUF.

LOOP - (40) this subroutine uses the next three words in the data buffer to create a repeating loop in the data buffer. The three words are -

- 1) a counter, incremented each repetition

- 2) maximum number of repetitions

- 3) (counter) to the top of the loop

Each time a loop command (40) is encountered in the data buffer, the loop subroutine first compares the counter with the maximum number of repetitions (line 1). If the counter is less than the maximum number the counter is incremented, the pointer to DBUF (third word in the parameter list) is updated with the pointer to the top of the loop, and return to the interpreter (lines 3-5). If the counter is equal to or greater than the counter we branch to LOOP 1 (line 2), clear the counter (line 6), step the data buffer pointer (line 7), and return to the interpreter (line 8).

- 1) LOOP: CMP (R1), 2 (R1)

- 2) BPL LOOP 1

- 3) INC (R1)

- 4) MOV 4 (R1), R1

- 5) RTS PC

- 6) LOOP 1: CLR (R1)

- 7) ADD #6, R1

8) RTS PC

Command words 41 - 45 are not used, therefore they are cross-referenced to the error routine ERR in JBUF. The error routine is in reality the exit routine -

EXIT - (47) this subroutine is invoked overtly by command word 47 and covertly by 06,07,25,26,27,36,37,41,42,43,44 and 45. It ends the program in a relatively painless manner and returns control to the system monitor using the .EXIT macro.

#### .EXIT

The input subroutine services these fourteen input devices -

- 1 8) 16 word data tables defined by user

- 9 12) analog to digital converters

- 13) real time interface

- 14) random number generator

The first part of the input routine retrieves data from the tables (input devices 1 - 8)

- 1) IN: MOV (R1) + , R2

- 2) CMP R2, #11

- 3) BPL IN1

- 4) MOV (R1) +, R3

- 5) DEC R2

- 6) ASL R2

- 7) ASL R2

| 8) | ASL | R2 |

|----|-----|----|

|    |     |    |

9) ASL R2

10) DEC R3

11) ASL R3

12) ADD R3 , R2

13) ADD #TABLES , R2

14) MOV (R2), R2

15) RTS PC

In line 1 the input device number is transferred from the data buffer to register 1, and the buffer pointer incremented. If the device number is greater than 8 branch to IN1 (lines 2 and 3). If not move the table entry number to register 2 and calculate the location of the data (lines 4 - 13) as follows -

location = # TABLES + 2 \* (entry number - 1) + 16 \* (device number - 1).

Finally register 2 transforms itself into the requested data (line 14) and

we return to the calling subroutine (line 15).

The second part of the input routine services the analog to digital converters (input devices 9 - 12) -

- 1) IN: CMP R2, # 15

- 2) BPL IN2

- 3) SUB # 11 , R2

- 4) MOV R2, @# LEWCHA

- 5) MOV @# LEWIN , R2

- 6) RTS PC

Again we test the device number. If greater than 12 branch to IN2 (lines 1 and 2). The channel address is calculated and moved to the control word LEWCHA (lines 3 and 4). The data appears at the input word LEWIN and is tramsferred to register 2 (line 5). We return to the calling subroutine (line 6).

The third part of the input routine service Don McArthur's real time interface (a register loaded from the outside world using toggle switches, input device 13).

- 1) IN2: CMP R2, # 16

- 2) BPL IN3

- 3) MOV @# DONIN , R2

- 4) RTS PC

A model of the efficiency of memory mapped I/O; but first we test the device number. If greater than 13 branch to IN3 (lines 1 and 2). In a single of code the data is transferred to register 2 (line 3) and we return to the calling subroutine. Good work Don!

The final section of the input routine is a random number generator of sorts (input device 14) -

| 1)  | IN3:  | CMP   | R2 , # 17 |

|-----|-------|-------|-----------|

| 2)  |       | BPL   | IN4       |

| 3)  |       | MOV   | TEMP , R2 |

| 4)  |       | CLC   |           |

| 5)  |       | ROL   | TEMP      |

| 6)  |       | ВСС   | RND1      |

| 7)  |       | INC   | R2        |

| 8)  | RND1: | ROL   | TEMP + 2  |

| 9)  |       | BCC   | RND2      |

| 10) |       | INC   | R2        |

| 11) | RND2: | ROL   | TEMP + 4  |

| 12) |       | ВСС   | RND3      |

| 13) |       | INC   | R2        |

| 14) | RND3: | ROL   | TEMP + 6  |

| 15) |       | ВСС   | RND4      |

| 16) |       | INC   | R2        |

| 17) | RND4: | COM   | R2        |

| 18) |       | ADD   | R2 , TEMP |

| 19) |       | MOV   | TEMP , R2 |

| 20) | IN4:  | RTS   | PC        |

| 21) | TEMP: | .WORD | 0,0,0,0   |

Test the device number, if greater than 14 return to the calling program via IN4 (lines 1, 2 and 20). Now we perform a left shift on TEMP (a giant 64 bit word). This is done in 4 steps (of 16 bits) through the

carry register (1 bit).

64 48 47 32 31 16 15 0

TEMP+6 TEMP+4 TEMP+2 TEMP

c3 c3 c2 c1

TEMP = TEMP + (-1) \* (TEMP + C4 + C3 + C2 + C1)

The initial value of TEMP is stored in register 2 and the carry register cleared (lines 3 and 4). Now the 4 shifts are executed and the resultant carrys added to register 2 (lines 5 - 16). We wrap it up (lines 17 and 18), move the low order 16 bits to register 2 (line 19), and return to where we came from (line 20). Space for the TEMP is created with the .WORD macro (line 21).

The output subroutine services these fifteen output devices -

- 1-8) digital to analog converters

- 9) red 16:1 select channels

- 10) green 16:1 select channels

- 11) blue 16:1 select channels

- 12) inversion register

- 13) red ALU (arithmetic logic unit)

- 14) green ALU

- 15) blue ALU

Through an unaccountable memtal lapse on my part, the data buffers correspond

directly to the output devices - data buffers 1-8 control the A/D's, data buffer 9 controls the red 16:1 select channels, and so on. The first part of the output routine controls the A/D's -

| 1) | OUT: | CMPB | TMRX , # 11        |

|----|------|------|--------------------|

| 2) |      | BPL  | OUT 1              |

| 3) |      | MOVB | TMRX , R2          |

| 4) |      | DEC  | R2                 |

| 5) |      | MOV  | R2 , @# LEWCHA     |

| 6) |      | MOV  | 6 (RO) , @# LEWOUT |

| 7) |      | INC  | R5                 |

| 8) |      | RTS  | PC                 |

If the buffer number is greater than 8 branch to OUT1 (lines 1 and 2).

If not calculate the channel address and move it to the control word

LEWCHA (lines 3 = 5). Next move the data to the output word LEWOUT, set

the done flag (register 5), and return to the calling program (lines 6-8).

The second part of the routine controls Don McArthur's 16:1 selects and inversion register -

| 1) | OUT1: | CMPB | TMRX | , | # 15 |

|----|-------|------|------|---|------|

| 2) |       | BPL  | OUT2 |   |      |

| 3) |       | MOVB | TMRX | , | R2   |

| 4) |       | SUB  | # 11 | , | R2   |

| 5) |       | ASL  | R2   |   |      |

| 6) | ADD | # DONOUT | . R2 |

|----|-----|----------|------|

|    |     |          |      |

- 7) MOV 6 (RO), (R2)

- 8) INC R5

- 9) RTS PC

If the buffer number is greater than 12 branch to OUT2 (lines 1 and 2).

If not calculate the output address (lines 3 - 6) -

output address = # DONOUT + 2 \* (TMRX - 9)

Finally we transfer the data word to output address, set the done flag line, and return to the calling program (lines 7 - 9).

Part three of the routine is similiar; it controls Jeff Shier's arithmetic logic units -

| 1) | OUT2: | CMPB | TMRX , #20    |

|----|-------|------|---------------|

| 2) |       | BPL  | OUT3          |

| 3) |       | MOVB | TMRX , R2     |

| 4) |       | SUB  | # 15 , R2     |

| 5) |       | ASL  | R2            |

| 6) |       | ADD  | # JEFOUT , R2 |

| 7) |       | MOV  | 6 (RO) , (R2) |

| 8) | OUT3: | INC  | R5            |

| 9) |       | RTS  | PC            |

|    |       |      |               |

If the buffer number is greater than 15, game over, we return to the calling program via OUT3 (lines 1,2,8 and 9). If not calculate the output address (lines 3 and 5) -

output address = # JEFOUT + 2 \* (TMRX-13)

Finally we output the data word, set the done flag, and return (lines 7-9).

In the program areas of memory are reserved for data buffers including -

- 1) EBUF the enable buffer indicates whether the data buffer is active.

- 2) PBUF the parameter list used by the timer and interpreter to access the data buffers.

- 3) TABLES used to store prepared data, accessed with the input subroutine (IN).

- 4) DBUF 1 15 sixteen data buffers containing sequences of command words which control the available input/output devices on the system.

EBUF

PBUF

DBUF 1

These data buffers become a seperate program which is linked to the main program by the system loader before execution. First we establish the globals identifying the labels common to both the main program and the data program -

.GLOBAL TABLES, EBUF, DBUF

There are eight tables of sixteen words (8 X 16 = 128). The following sequence of code will reserve memory for the tables.

- 1) TABLES:

- 2) TBL1:

- 3) . = TABLES + 20

- 4) TBL2:

- 5) . = TABLES + 40

- 6) TBL3:

- 7) . = TABLES + 60

- 8) TBL4:

- 9) . = TABLES + 100

- 10) TBL5:

- 11) . = TABLES + 120

- 12) TBL6:

- 13) . = TABLES + 140

- 14) TBL7:

- 15) . = TABLES + 160

- 16) TBL8:

- 17) . = TABLES + 200

Note the first two labes are synonymous (TABLES and TABLI lines 1 and 2) for convenience. After each table heading (TBL1, TBL2, etc) a block of sixteen words is reserved by setting the program counter (.) to the next heading or label (line 3, etc).

Tables are filled in as illustrated in the following example -

| 1) | TBL1: | .WORD | 104210 |

|----|-------|-------|--------|

| -, |       |       |        |

- 2) .WORD 177777

- 3) .WORD 167356

- 4) .WORD 156735

- 5) .WORD 146314

- 6) .WORD 135673

- 7) .WORD 125252

- 8) .WORD 114631

- 9) .WORD 73567

- 10) .WORD 63146

- 11) .WORD 52525

- 12) .WORD 42104

- 13) .WORD 31463

- 14) .WORD 21042

- 15) .WORD 10421

- 16) .WORD 0

This table contains the simplest bar patterns available on Don McArthur's 16:1 select modules.

- line 1) represents a solid field

- line 2) two horizontal bars

- line 3) four horizontal bars

- line 4) eight horizontal bars

- line 5) sixteen horizontal bars

- line 6) thirty-two horizontal bars

- line 7) sixty-four horizontal bars

- line 8) one hundred and twenty-eight horizontal bars

- line 9) two vertical bars

- line 10) four vertical bars

- line 11) eight vertical bars

- line 12) sixteen vertical bars

- line 13) thirty-two vertical bars

- line 14) sixty-four vertical bars

- line 15) one hundred and twenty-eight vertical bars

- line 16) two hundred and fifty-six vertical bars

Other tables are useful - shaded bar patterns, crosshatch patterns, and masks for example.

Following the tables is the enable buffer (EBUF), a short buffer of sixteen bytes (eight words) set 0 for an inactive buffer, and 1 for an active buffer.

- 1) EBUF: .BYTE 0,0,0,0,0,0,0

- 2) .BYTE 1,1,1,0,0,0,0

- 3) . = EBUF + 10

In the example only buffers 9,10,11 and 12 are active and the remainder inactive. The block of eight words is created (lines 1 and 2) and the program counter set to the next label (line 3).

Now we reserve memory for the sixteen data buffers as follows -

- 1) DBUF:

- 2) DBUF1:

- 3) . = DBUF + 400

- 4) DBUF2:

- 5) . = DBUF + 1000

- 6) DBUF3:

- 7) . = DBUF + 1400

- 8) DBUF4:

- 9) . = DBUF + 2000

- 10) DBUF5: - I LOF + 2400

- 11) . = DBUF + 2400

- 12) DBUF6:

- 13) . = DBUF + 3000

- 14) DBUF7: